The Clock Divider is a dual module that slows incoming clock pulses by a factor of two to sixteen. The modules can run independently from one another or be linked so that the clock input and reset jacks from the first module are shared by both.

So what does it mean to divide a clock signal?

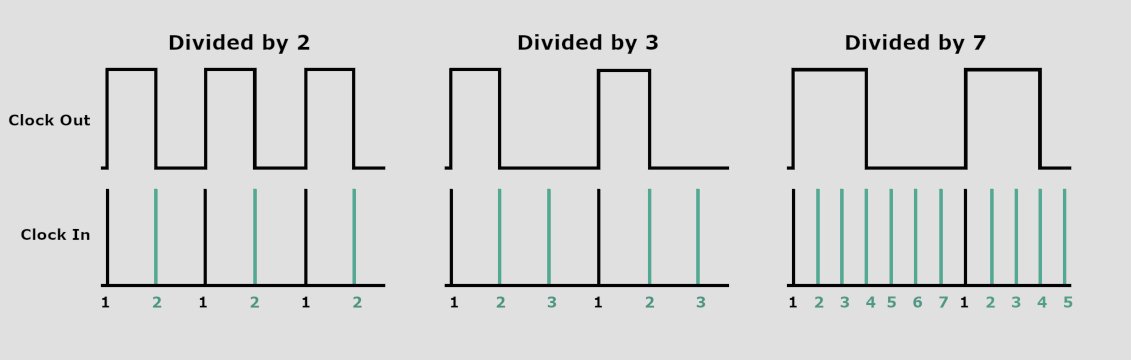

When a clock signal is divided, the timing of its pulses are not changed. Instead, the Clock Divider creates a new pulse-wave signal that represents only a fraction of the pulses received at the input.

Let’s look at a sixteenth-note clock signal as an example. Dividing by a factor of two means that one pulse is output for every two pulses received resulting in an eighth note clock signal. Dividing by a factor of three means that one pulse is output for every three received which is the equivalent of dotted-eighth notes. Dividing by a factor of seven doesn’t result in a common note duration, but the same principle is used. The divider only outputs one pulse for every seven pulses which by the way can create some really cool poly-rhythms!

It is worth noting that the input signal doesn’t need to be a designated clock signal. Any voltage transition from below 2.5V to 2.5V or higher will be interpreted as a pulse meaning you can use an LFO, the gate signal from a MIDI controller, or even an audio signal!

Inputs, Outputs and Controls

In jack- Input jack for the clock signal that will be divided. When the modules are linked the input signal from module one is internally routed to module two.

Reset jack- A 5V pulse or gate signal received at this jack will force the divided clock signal to restart on the next pulse received at the input jack. When the modules are linked the reset jack from module one will reset module two as well.

Divide By- This is the factor by which the clock signal will be divided. It can be set from one to sixteen by clicking on the up and down arrows to the left of the number display. A Divide By factor of one means the clock input will be unchanged (because duh, anything divided by one is itself!) but is a convenient way to temporarily bypass any clock division. A factor of two means one pulse is output for every two pulses received at the input. A factor of nine means one pulse is output for every nine pulses. You get the idea.

Out jack- Outputs the divided clock signal.

Input Link- When engaged, the input and reset jacks from module one are sent internally to module two. If a cable is patched to either of module two’s inputs, the signal from the cable will “override” the link.